- 您现在的位置:买卖IC网 > Sheet目录2004 > LTC1660IN (Linear Technology)IC D/A CONV 10BIT OCTAL 16-DIP

LTC1665/LTC1660

10

166560fa

OPERATION

Sleep Mode

DAC address 1110bisreservedforthespecialSleepinstruc-

tion (see Table 2). In this mode, the digital interface stays

active while the analog circuits are disabled; static power

consumption is thus virtually eliminated. The reference

input and analog outputs are set in a high impedance state

and all DAC settings are retained in memory so that when

Sleep mode is exited, the outputs of DACs not updated by

the Wake command are restored to their last active state.

DIN

DOUT

SCK

CS/LD

A3

A2

INPUT WORD W0

INPUT CODE

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

X3

X2

X1

X0

A3

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

X3

X2

X1

X0

A3

166560 F02a

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

(ENABLE CLK)

(UPDATE OUTPUT)

ADDRESS/CONTROL

DON’T CARE

INPUT WORD W0

INPUT WORD W–1

DIN

DOUT

SCK

CS/LD

A3

A2

INPUT WORD W0

INPUT CODE

DON’T CARE

A1

A0

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

X1

X0

A3

A2

A1

A0

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

X1

X0

A3

166560 F02b

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

(ENABLE CLK)

(UPDATE OUTPUT)

ADDRESS/CONTROL

INPUT WORD W0

INPUT WORD W–1

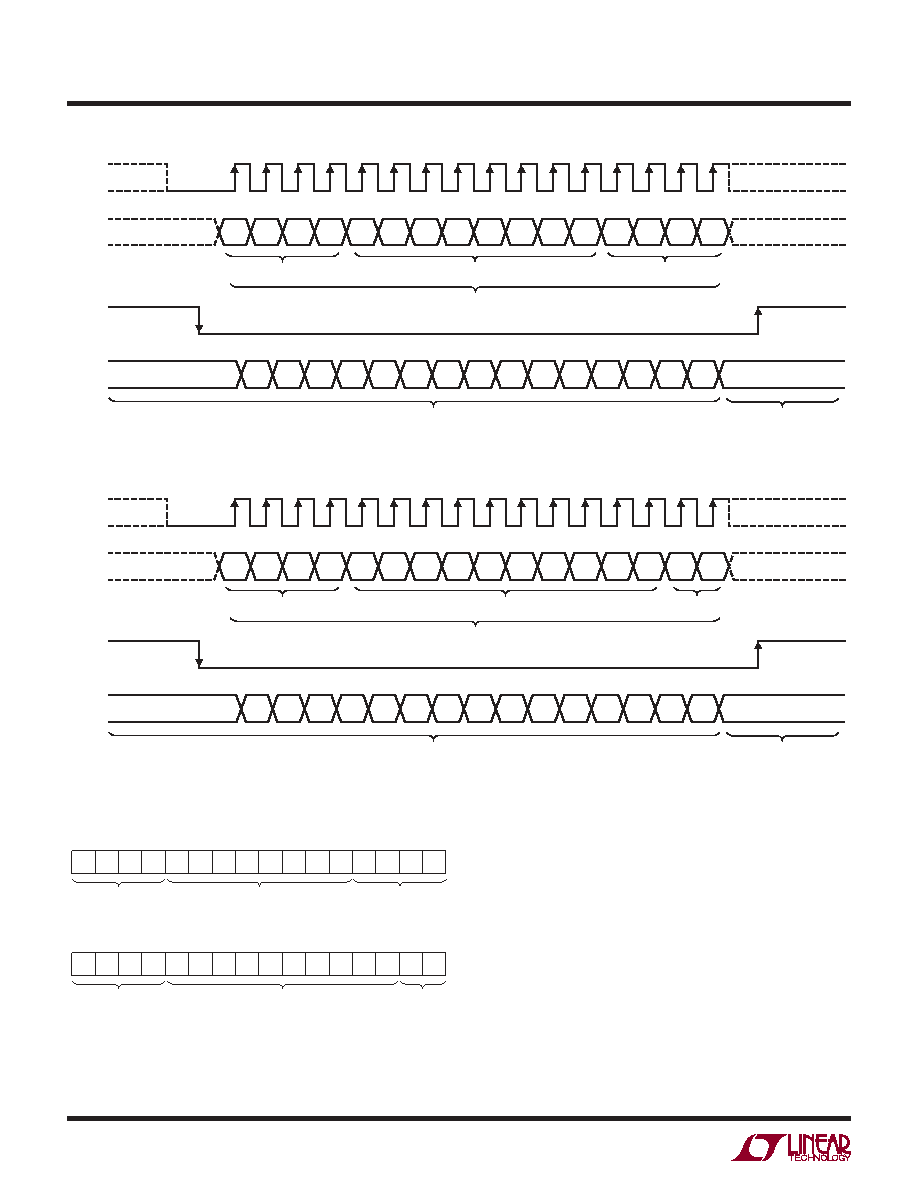

Figure 2a. LTC1665 Register Loading Sequence

Figure 2b. LTC1660 Register Loading Sequence

Table 1a. LTC1665 Input Word

Table 1b. LTC1660 Input Word

A3 A2 A1

ADDRESS/CONTROL

A0 D9 D8 D7 D6 D5 D4 D3 D2 D1

X1 X0

D0

INPUT CODE

DON’T

CARE

A3 A2 A1

ADDRESS/CONTROL

A0 D7 D6 D5 D4 D3 D2 D1 D0 X3

X1 X0

X2

DON’T CARE

INPUT CODE

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

LTC1661IMS8#TRPBF

IC D/A CONV 10BIT MICRPWR 8-MSOP

LTC1662IN8#PBF

IC D/A CONV 10BIT MICRPWR 8-DIP

LTC1663-1CS5#TRM

IC DAC 10BIT R-R TSOT23-5

LTC1664IN

IC DAC 10BIT QUAD MICRPWR 16DIP

LTC1667CG#PBF

IC D/A CONV 14BIT 50MSPS 28-SSOP

LTC1686IS8#TRPBF

IC TXRX RS485 PREC DELAY 8-SOIC

LTC1688IS

IC DVR 100MBPS RS485 QUAD 16SOIC

LTC1690IS8#TRPBF

IC RCVR/DVR PAIR LOW PWR 8-SOIC

相关代理商/技术参数

LTC1660IN#PBF

功能描述:IC D/A CONV 10BIT OCTAL 16-DIP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):*

LTC1661CMS8

功能描述:IC D/A CONV 10BIT MICRPWR 8-MSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 设计资源:Unipolar, Precision DC Digital-to-Analog Conversion using AD5450/1/2/3 8-14-Bit DACs (CN0052)

Precision, Bipolar, Configuration for AD5450/1/2/3 8-14bit Multiplying DACs (CN0053)

AC Signal Processing Using AD5450/1/2/3 Current Output DACs (CN0054)

Programmable Gain Element Using AD5450/1/2/3 Current Output DAC Family (CN0055)

Single Supply Low Noise LED Current Source Driver Using a Current Output DAC in the Reverse Mode (CN0139) 标准包装:10,000 系列:- 设置时间:- 位数:12 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:SOT-23-8 薄型,TSOT-23-8 供应商设备封装:TSOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):2.7M

LTC1661CMS8#PBF

功能描述:IC D/A CONV 10BIT MICRPWR 8-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:3,000 系列:nanoDAC™ 设置时间:80µs 位数:18 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:SOT-23-8 供应商设备封装:SOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电压,单极 采样率(每秒):- 产品目录页面:784 (CN2011-ZH PDF) 配用:EVAL-AD5680EBZ-ND - BOARD EVAL FOR AD5680 其它名称:AD5680BRJZ-2REEL7TR

LTC1661CMS8#TR

功能描述:IC DAC 10BIT DUAL MICROPWR 8MSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 设计资源:Unipolar, Precision DC Digital-to-Analog Conversion using AD5450/1/2/3 8-14-Bit DACs (CN0052)

Precision, Bipolar, Configuration for AD5450/1/2/3 8-14bit Multiplying DACs (CN0053)

AC Signal Processing Using AD5450/1/2/3 Current Output DACs (CN0054)

Programmable Gain Element Using AD5450/1/2/3 Current Output DAC Family (CN0055)

Single Supply Low Noise LED Current Source Driver Using a Current Output DAC in the Reverse Mode (CN0139) 标准包装:10,000 系列:- 设置时间:- 位数:12 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:SOT-23-8 薄型,TSOT-23-8 供应商设备封装:TSOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):2.7M

LTC1661CMS8#TRPBF

功能描述:IC D/A CONV 10BIT MICRPWR 8-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 设计资源:Unipolar, Precision DC Digital-to-Analog Conversion using AD5450/1/2/3 8-14-Bit DACs (CN0052)

Precision, Bipolar, Configuration for AD5450/1/2/3 8-14bit Multiplying DACs (CN0053)

AC Signal Processing Using AD5450/1/2/3 Current Output DACs (CN0054)

Programmable Gain Element Using AD5450/1/2/3 Current Output DAC Family (CN0055)

Single Supply Low Noise LED Current Source Driver Using a Current Output DAC in the Reverse Mode (CN0139) 标准包装:10,000 系列:- 设置时间:- 位数:12 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:SOT-23-8 薄型,TSOT-23-8 供应商设备封装:TSOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):2.7M

LTC1661CMS8PBF

制造商:Linear Technology 功能描述:DAC 10-Bit Rail-to-Rail Micropower MSOP8

LTC1661CN8

功能描述:IC D/A CONV 10BIT MICRPWR 8-DIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 设计资源:Unipolar, Precision DC Digital-to-Analog Conversion using AD5450/1/2/3 8-14-Bit DACs (CN0052)

Precision, Bipolar, Configuration for AD5450/1/2/3 8-14bit Multiplying DACs (CN0053)

AC Signal Processing Using AD5450/1/2/3 Current Output DACs (CN0054)

Programmable Gain Element Using AD5450/1/2/3 Current Output DAC Family (CN0055)

Single Supply Low Noise LED Current Source Driver Using a Current Output DAC in the Reverse Mode (CN0139) 标准包装:10,000 系列:- 设置时间:- 位数:12 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:SOT-23-8 薄型,TSOT-23-8 供应商设备封装:TSOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):2.7M

LTC1661CN8#PBF

功能描述:IC D/A CONV 10BIT MICRPWR 8-DIP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:3,000 系列:nanoDAC™ 设置时间:80µs 位数:18 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:SOT-23-8 供应商设备封装:SOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电压,单极 采样率(每秒):- 产品目录页面:784 (CN2011-ZH PDF) 配用:EVAL-AD5680EBZ-ND - BOARD EVAL FOR AD5680 其它名称:AD5680BRJZ-2REEL7TR